۰

subtitle

ارسال: #۱

تبدیل عدد ممیزدار باینری به عدد اعشاری در vhdl

سلام.

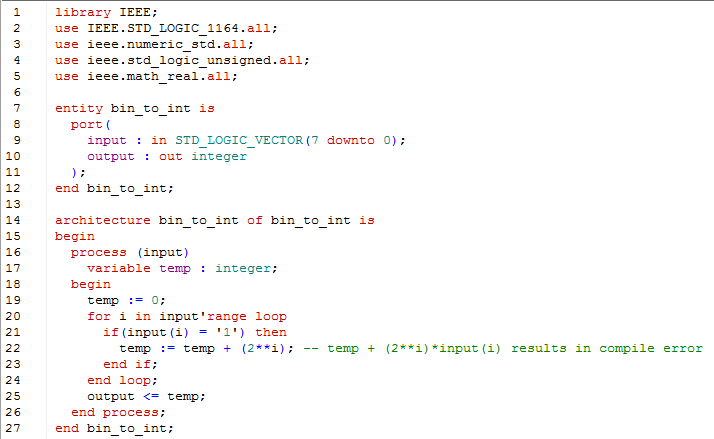

برنامه ای که نوشته شده، برای تبدیل عدد ممیزدار باینری به عدد اعشاری است که در یک حلقه for از سمت چپ ترین بیت شروع به ضرب ان در ارززشش میشه.یعنی از سمت چپ هر عدد باید در ارزشش ضرب شود و با مقدار قبلی جمع شود.ولی خطا میدهد. ؟؟ایراد چی هست؟

![[تصویر: 373102_2bcx_img-20150712-wa0014.jpg]](https://img.manesht.ir/373102_2bcx_img-20150712-wa0014.jpg)

برنامه ای که نوشته شده، برای تبدیل عدد ممیزدار باینری به عدد اعشاری است که در یک حلقه for از سمت چپ ترین بیت شروع به ضرب ان در ارززشش میشه.یعنی از سمت چپ هر عدد باید در ارزشش ضرب شود و با مقدار قبلی جمع شود.ولی خطا میدهد. ؟؟ایراد چی هست؟

![[تصویر: 373102_2bcx_img-20150712-wa0014.jpg]](https://img.manesht.ir/373102_2bcx_img-20150712-wa0014.jpg)

۱

ارسال: #۲

RE: تبدیل عدد ممیزدار باینری به عدد اعشاری در vhdl

(۲۱ تیر ۱۳۹۴ ۰۵:۱۹ ب.ظ)The BesT نوشته شده توسط: سلام.

برنامه ای که نوشته شده، برای تبدیل عدد ممیزدار باینری به عدد اعشاری است که در یک حلقه for از سمت چپ ترین بیت شروع به ضرب ان در ارززشش میشه.یعنی از سمت چپ هر عدد باید در ارزشش ضرب شود و با مقدار قبلی جمع شود.ولی خطا میدهد. ؟؟ایراد چی هست؟

سلام

کاربرد generate اینجا نیست که.

ارسال: #۳

RE: تبدیل عدد ممیزدار باینری به عدد اعشاری در vhdl

(۲۱ تیر ۱۳۹۴ ۱۱:۳۷ ب.ظ)behnam5670 نوشته شده توسط:ممنون ولی مگر توان دو نباید i منهای ۸ باشد؟ اما وقتی ورودی داده میشود خطا میدهد.و در برنامه خروجی راreal تعریف کردیم ولی باز هم خطا میدهد(21 تیر ۱۳۹۴ ۰۵:۱۹ ب.ظ)The BesT نوشته شده توسط: سلام.

برنامه ای که نوشته شده، برای تبدیل عدد ممیزدار باینری به عدد اعشاری است که در یک حلقه for از سمت چپ ترین بیت شروع به ضرب ان در ارززشش میشه.یعنی از سمت چپ هر عدد باید در ارزشش ضرب شود و با مقدار قبلی جمع شود.ولی خطا میدهد. ؟؟ایراد چی هست؟

سلام

کاربرد generate اینجا نیست که.

ارسال: #۴

RE: تبدیل عدد ممیزدار باینری به عدد اعشاری در vhdl

فکر کنم همچین چیزی مد نظرتون بود:

تنها مشکل احتمالی میتونه این باشه که نوع دادهی real از توان منفی پشتیبانی نکنه (البته در زمان کامپایل متوجه نخواهد شد) که در اون صورت به شکلی که مقابلش کامنت کردم بنویسید، و یا از نوع دادهی float استفاده کنید که لایبری و پکیجاش بستگی به ورژن VHDL و ابزار شبیهسازیتون داره.

کد:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use ieee.numeric_std.all;

use ieee.std_logic_unsigned.all;

use ieee.math_real.all;

entity bin_to_int is

port(

input : in STD_LOGIC_VECTOR(7 downto 0);

output : out real

);

end bin_to_int;

architecture bin_to_int of bin_to_int is

begin

process (input)

variable temp : real;

begin

temp := 0.0;

for i in input'range loop

if(input(i) = '1') then

temp := temp + real(2**(i-8)); --temp := temp + real(1/(2**(8-i)));

end if;

end loop;

output <= temp;

end process;

end bin_to_int;تنها مشکل احتمالی میتونه این باشه که نوع دادهی real از توان منفی پشتیبانی نکنه (البته در زمان کامپایل متوجه نخواهد شد) که در اون صورت به شکلی که مقابلش کامنت کردم بنویسید، و یا از نوع دادهی float استفاده کنید که لایبری و پکیجاش بستگی به ورژن VHDL و ابزار شبیهسازیتون داره.

Can I see some ID?

Feeling left out?

نگران نباش، فقط روی این لینک برای ثبت نام کلیک کن. رمزت رو فراموش کردی؟ اینجا به یادت میاریم! close