۰

subtitle

ارسال: #۱

۲ سوال معماری (RTL و سیم Bus مشترک)

سلام دوستان. برای امتحان پایانی یه سری نمونه سوال دادن. یکیش اینه.

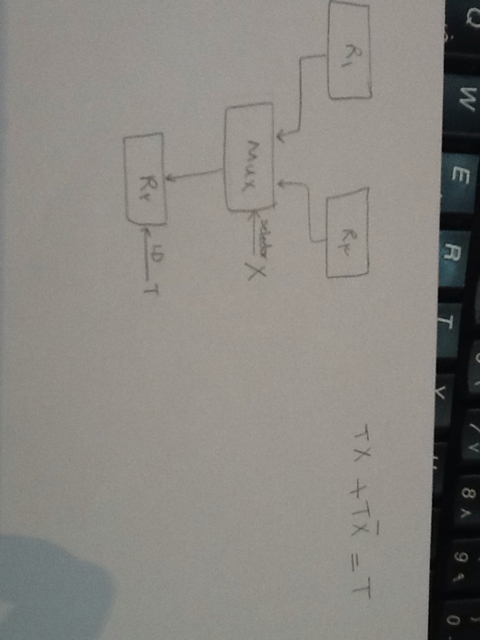

میشه لطفا پاسخش رو کمک کنید پیدا کنم؟ خیلی ممنونم. تو RTL وقتی مثلا میگن ۲ تا رو جمع کنه و به یکی بریزه رو میفهمم و بلدم. ولی این سوال صورتش برام واضح نیست. قاعدتا منظورش این نیست که فقط R1 به R2 بره و R3 به R2؟ و اینکه X دومی not هست.

![[تصویر: 290671_cvu1tvxa55seof25vbwd.jpg]](https://img.manesht.ir/290671_cvu1tvxa55seof25vbwd.jpg)

سوال دوم اینه:

![[تصویر: 290671_emrar7jbb2xcx0wgq2dh.jpg]](https://img.manesht.ir/290671_emrar7jbb2xcx0wgq2dh.jpg)

مربوط میشه به سیم گذرگاه مشترک. یعنی این شکل:

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

از روی این چطور میشه جواب رو پیدا کرد؟ خیلی ممنونم از لطفتون.

میشه لطفا پاسخش رو کمک کنید پیدا کنم؟ خیلی ممنونم. تو RTL وقتی مثلا میگن ۲ تا رو جمع کنه و به یکی بریزه رو میفهمم و بلدم. ولی این سوال صورتش برام واضح نیست. قاعدتا منظورش این نیست که فقط R1 به R2 بره و R3 به R2؟ و اینکه X دومی not هست.

![[تصویر: 290671_cvu1tvxa55seof25vbwd.jpg]](https://img.manesht.ir/290671_cvu1tvxa55seof25vbwd.jpg)

سوال دوم اینه:

![[تصویر: 290671_emrar7jbb2xcx0wgq2dh.jpg]](https://img.manesht.ir/290671_emrar7jbb2xcx0wgq2dh.jpg)

مربوط میشه به سیم گذرگاه مشترک. یعنی این شکل:

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

از روی این چطور میشه جواب رو پیدا کرد؟ خیلی ممنونم از لطفتون.

۱

ارسال: #۲

۲ سوال معماری (RTL و سیم Bus مشترک)

(۲۷ مرداد ۱۳۹۳ ۰۹:۵۰ ق.ظ)reza_a نوشته شده توسط: لطفا اگر کوچکترین آشنایی و اطلاعی دارین کمک کنین. همه نمره بستگی به این سوال ها داره. خیلی ممنونم.

ببینین برای این سوال چون دو مقدار میخواد وارد R2 بشه احتیاج به مالتیپلکسر داریم، لود R2 هم با دو حالت فعال میشه که ما بینش باید or بگیریم و وقتی or میگیریم مقدار نهاییش همون t میشه یعنی لودش همون t هست، اما سلکتور مالتیپلکسر رو x در نظر میگیریم که اگر یک باشه مثلا r3 وارد شه و اگر صفر باشه r1 وارد شه، اما نمیدونم فلسفه ی اون خط اخری که t رو نوشته چیه، همینیه که من میگم یا منظورش فرق داره

۰

ارسال: #۳

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

سوال اول رو درست جواب دادن. اون T لودی که اضافه کرده در واقع قسمتی از جوابه که آوا جان فرمودن.

- توضیح اضافه سوال اولتون:

اگه بین ثبات ها (Rها) اتصال باشه و پایه ی load ثبات مقصد (R1)فعال (۱)باشه, در اون صورت میشه محتوای مثلا R2 رو ریخت تو R1 (چرا نشه? !)

-سوال دوم.دو تا اتفاق افتاده. یه عمل جمع (عملی محاسباتی نیازمند مدار ALU ) و یه عمل انتقال (حاصلجمع ریخته بشه توی AC که نیازمند فعال بودن پایه لود AC هست)

(همیشه اول این سوال رو بپرس) باید ببینیم طبق معماری داده شده این عملیات قابل انجامه? شکل رو ببینید و بگید آیا M(AR) - که یه خونه از حافظه هست- مثل AC مستقیم به ALU وصله? جواب نه است. خروجی حافظه به bus وصله نهALU. پس باید قبل از هر چیز, m(AR) رو (به وسیله bus) بریزم توی DR (چون به واحد محاسبه وصله)

ریزعملام:

: fetch

: Decode

: DR <- M(AR)

: AC <- AC + DR

چه موقع جمع انجام میشه? این رو فاز دیکد مشخص میکنه. شما یه سیگنال به اسم Yرو نماینده عملیات جمع بگیر.

تا اینجا:

Y: DR <- M(AR)

Y: AC <- AC + DR

اما این نمیتونه تنها سیگنال من باشه. ببینید تو سوال اول مگه میشه در یک لحظه (در یک واحد کوچک زمان. در یک کلاک) هم زمان دو تا ثبات مختلف رو تو یک ثبات ریخت? این عمل حتما باید در دو زمان متفاوت انجام بشه. (اگه اولی داشت کپی میشد, دومین خط اجرا نشه) برای همین یه سیگنال کنترلی مثل x تعریف شد و not اش رو داد به خط دومی. (که اگه یک شد فقط خط بالا و اگه صفر شد فقط خط پایین داخلR2 لود بشن.)

توی این سوالم تقریبا چنین مشکل هست (اجرا نشدن همزمان). مگه میشه DR رو هم زمان, هم ازش خوند (توی جمع) و هم روش نوشت (انتقال محتویات حافظه بهش)?

مسلما نه! پس باید توی دوتا زمان (پشت سر هم) که همون کلاک هست اجرا بشن.

مثلا این شکلی:

Y.T1 : DR <- M(AR)

Y.T2 : AC <- AC + DR

توضیحات اضافه:

سیگنالای کنترلی رو اگه میخوای تعیینش کنی باید بدونی چرا اصلا لازمه!

برای جمع, اولا یه سیگنال کنترلی باید به ALU بگه اوپرند اول و دومی که بهت وارد میشه رو جمع کن. (منها یا کار دیگه نکن)

یه سیگنال فعال کننده لازمه که خروجی ۷ bus فعال شه (تا حافظه بیاد رو باس شناور شه و با لود DR منتقل شه توش)

یه سری سیگنالم باید پایه لود AC و DRرو فعال کنه برای انتقالات.

یعنی هر وقت میخوام حافظه رو با آکومولیتور جمع کنم,باید حتما این سیگنالارو (T1 وT2 وY) وصل کنم به پایه کنترل ALU و لود ثباتا. (یعنی تو سخت افزار, سیم کشی میکنم و طبق توابع کنترلی مدار منطقی میکشم وصل میکنم به اون پایه ها)

- توضیح اضافه سوال اولتون:

اگه بین ثبات ها (Rها) اتصال باشه و پایه ی load ثبات مقصد (R1)فعال (۱)باشه, در اون صورت میشه محتوای مثلا R2 رو ریخت تو R1 (چرا نشه? !)

-سوال دوم.دو تا اتفاق افتاده. یه عمل جمع (عملی محاسباتی نیازمند مدار ALU ) و یه عمل انتقال (حاصلجمع ریخته بشه توی AC که نیازمند فعال بودن پایه لود AC هست)

(همیشه اول این سوال رو بپرس) باید ببینیم طبق معماری داده شده این عملیات قابل انجامه? شکل رو ببینید و بگید آیا M(AR) - که یه خونه از حافظه هست- مثل AC مستقیم به ALU وصله? جواب نه است. خروجی حافظه به bus وصله نهALU. پس باید قبل از هر چیز, m(AR) رو (به وسیله bus) بریزم توی DR (چون به واحد محاسبه وصله)

ریزعملام:

: fetch

: Decode

: DR <- M(AR)

: AC <- AC + DR

چه موقع جمع انجام میشه? این رو فاز دیکد مشخص میکنه. شما یه سیگنال به اسم Yرو نماینده عملیات جمع بگیر.

تا اینجا:

Y: DR <- M(AR)

Y: AC <- AC + DR

اما این نمیتونه تنها سیگنال من باشه. ببینید تو سوال اول مگه میشه در یک لحظه (در یک واحد کوچک زمان. در یک کلاک) هم زمان دو تا ثبات مختلف رو تو یک ثبات ریخت? این عمل حتما باید در دو زمان متفاوت انجام بشه. (اگه اولی داشت کپی میشد, دومین خط اجرا نشه) برای همین یه سیگنال کنترلی مثل x تعریف شد و not اش رو داد به خط دومی. (که اگه یک شد فقط خط بالا و اگه صفر شد فقط خط پایین داخلR2 لود بشن.)

توی این سوالم تقریبا چنین مشکل هست (اجرا نشدن همزمان). مگه میشه DR رو هم زمان, هم ازش خوند (توی جمع) و هم روش نوشت (انتقال محتویات حافظه بهش)?

مسلما نه! پس باید توی دوتا زمان (پشت سر هم) که همون کلاک هست اجرا بشن.

مثلا این شکلی:

Y.T1 : DR <- M(AR)

Y.T2 : AC <- AC + DR

توضیحات اضافه:

سیگنالای کنترلی رو اگه میخوای تعیینش کنی باید بدونی چرا اصلا لازمه!

برای جمع, اولا یه سیگنال کنترلی باید به ALU بگه اوپرند اول و دومی که بهت وارد میشه رو جمع کن. (منها یا کار دیگه نکن)

یه سیگنال فعال کننده لازمه که خروجی ۷ bus فعال شه (تا حافظه بیاد رو باس شناور شه و با لود DR منتقل شه توش)

یه سری سیگنالم باید پایه لود AC و DRرو فعال کنه برای انتقالات.

یعنی هر وقت میخوام حافظه رو با آکومولیتور جمع کنم,باید حتما این سیگنالارو (T1 وT2 وY) وصل کنم به پایه کنترل ALU و لود ثباتا. (یعنی تو سخت افزار, سیم کشی میکنم و طبق توابع کنترلی مدار منطقی میکشم وصل میکنم به اون پایه ها)

ارسال: #۴

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

خیلی خیلی ممنونم از هر دو شما بزرگوار. واقعا لطف کردین. الان پاسخ هارو میخوام بنویسم روی کاغذ که دقیق بخونم.

بعد با شرمندگی یک سوال دیگه هم بود. خودم حل کردم ولی احساس میکنم اشتباه حل کردم. صورت سوال و جوابی که به دست آوردم رو میذارم ممنون میشم بگید درسته یا نه. با تشکر

![[تصویر: 291051_6pyko5ukofsuuy5bpvwl.jpg]](https://img.manesht.ir/291051_6pyko5ukofsuuy5bpvwl.jpg)

بعد با شرمندگی یک سوال دیگه هم بود. خودم حل کردم ولی احساس میکنم اشتباه حل کردم. صورت سوال و جوابی که به دست آوردم رو میذارم ممنون میشم بگید درسته یا نه. با تشکر

![[تصویر: 291051_6pyko5ukofsuuy5bpvwl.jpg]](https://img.manesht.ir/291051_6pyko5ukofsuuy5bpvwl.jpg)

۰

ارسال: #۵

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

لطفا اگر کوچکترین آشنایی و اطلاعی دارین کمک کنین. همه نمره بستگی به این سوال ها داره. خیلی ممنونم.

۰

ارسال: #۶

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

این سوالی که دادین خودم توش مشکل دارم. (یعنی همیشه بی دقتی میکنم)

الان جوابتون به نظر من درسته

۸۱۹۲ کلمه ۱۳ بیت آدرس میخواد. ۱۶ ثبات ۴ بیت میخواد. ۲ مد آد رسم یه بیت بستشه. کلمات حافظه هم که ۳۲ بیتیه. پس قاعدتا جواب شما کاملا درسته! (بازم با کس دیگه چک کنید)

الان جوابتون به نظر من درسته

۸۱۹۲ کلمه ۱۳ بیت آدرس میخواد. ۱۶ ثبات ۴ بیت میخواد. ۲ مد آد رسم یه بیت بستشه. کلمات حافظه هم که ۳۲ بیتیه. پس قاعدتا جواب شما کاملا درسته! (بازم با کس دیگه چک کنید)

ارسال: #۸

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

خیلی معذرت میخوام یه سوال دیگه هم هست که آخریش هست. خیلی ممنون میشم این رو هم راهنمایی کنید. کلا صورت سوال رو من متوجه نمیشم. یعنی اصلا منظورش چیه؟ چی میخواد؟ دیکودر میخواد؟ یا مالتی پلکسر؟ یا جمع کننده؟ یا شمارنده؟ در مجموع اگر بگید اصلا سوالش منظورش چیه ممنون میشم. اینه صورت سوال:

برای طراحی یک باس مشترک که تعداد ۳۲ ثبات ۱۶ بیتی را بهم وصل میکند سخت افزارهای لازم را طراحی کنید.

برای طراحی یک باس مشترک که تعداد ۳۲ ثبات ۱۶ بیتی را بهم وصل میکند سخت افزارهای لازم را طراحی کنید.

۰

ارسال: #۱۰

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

۰

ارسال: #۱۱

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

برای ساخت باس مشترک برای m ثبات n بیتی نیاز با [tex]n\: Mux\: 2^{\lceil\lg\: m\rceil}\times1[/tex] است

ارسال: #۱۲

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

۰

ارسال: #۱۳

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

باس اگه اسم دومی داشت میشد "انتخابگر". باس برای چی تو مجموعه هست? برای اینکه ثبات ها با هم دعواشون نشه. در هر لحظه فقط و فقط "یک" ثبات "انتخاب" و روی خروجی باس شناور بشه. (برای هر جور انتقال و عملیاتی)

بین مدارایی که میشناسید هم فقط مالتی پلکسر هست که خاصیت انتخاب کردن رو داره. (بافر سه حالته هم هست که تو همون مانو خوب توضیحش داده. اینو بلد باشین اون اوکی هست)

قراره یه ثبات رو(از بین ۳۲ تا) به وسیله مالتی پلکسر انتخاب کنم. مسله اینجاست که ثبات های من یدونه بیت نیستن که بیان رو خروجی تک بیتی mux. هر ثبات ۱۶ بیته. پس باید هر دفعه یه دسته ۱۶ تایی از صفر و یک ها رو انتخاب کنم و بدم به خروجی.

بنابراین! باس من (که از مالتی پلکسرها ساخته شده) باید جوری باشه که ۱۶ تا بیته مربوط به یک ثبات رو (مثلا ۱۶ بیت ثبات A) "با هم" انتخاب کنه.

حالا چجوری.

ببینید خروجی من یه رشته ۱۶ بیتی از ۰ و۱ هاست. ناچارم برای هر بیت, یدونه مالتی پلکسر بذارم.

ارزش و جایگاه بیت های باینری از lsb تاmsb میشه بیت صفر, بیت ۱, بیت ۲ الی آخر (۲^۰/ ۲^۱/ ۲^۲/ ۲^۴/ ...)

طراحی من این خواهد بود:

از بین بیت های صفر ثباتهای داده شده, (کم ارزش ترین, lsb) یکی انتخاب شود. (۳۲ تا بیت در جایگاه صفر دارم, -چون ۳۲ ثبات داری- پس mux 32 *1)

از بین بیت های ۱, یکیشون انتخاب شود. (به همون دلیل بالا mux 32*1 )

به همین ترتیب تا آخر.

کافیه پ تا سیم سلکت های این ۱۶ تا mux رو به هم وصل کنی تا بیت های ثبات خروجی به دست بیاد (مثلا بیت صفر از R1 نیاد بیت یک از R2)

عکس ها رو ببینید

پیوست ها:

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

بین مدارایی که میشناسید هم فقط مالتی پلکسر هست که خاصیت انتخاب کردن رو داره. (بافر سه حالته هم هست که تو همون مانو خوب توضیحش داده. اینو بلد باشین اون اوکی هست)

قراره یه ثبات رو(از بین ۳۲ تا) به وسیله مالتی پلکسر انتخاب کنم. مسله اینجاست که ثبات های من یدونه بیت نیستن که بیان رو خروجی تک بیتی mux. هر ثبات ۱۶ بیته. پس باید هر دفعه یه دسته ۱۶ تایی از صفر و یک ها رو انتخاب کنم و بدم به خروجی.

بنابراین! باس من (که از مالتی پلکسرها ساخته شده) باید جوری باشه که ۱۶ تا بیته مربوط به یک ثبات رو (مثلا ۱۶ بیت ثبات A) "با هم" انتخاب کنه.

حالا چجوری.

ببینید خروجی من یه رشته ۱۶ بیتی از ۰ و۱ هاست. ناچارم برای هر بیت, یدونه مالتی پلکسر بذارم.

ارزش و جایگاه بیت های باینری از lsb تاmsb میشه بیت صفر, بیت ۱, بیت ۲ الی آخر (۲^۰/ ۲^۱/ ۲^۲/ ۲^۴/ ...)

طراحی من این خواهد بود:

از بین بیت های صفر ثباتهای داده شده, (کم ارزش ترین, lsb) یکی انتخاب شود. (۳۲ تا بیت در جایگاه صفر دارم, -چون ۳۲ ثبات داری- پس mux 32 *1)

از بین بیت های ۱, یکیشون انتخاب شود. (به همون دلیل بالا mux 32*1 )

به همین ترتیب تا آخر.

کافیه پ تا سیم سلکت های این ۱۶ تا mux رو به هم وصل کنی تا بیت های ثبات خروجی به دست بیاد (مثلا بیت صفر از R1 نیاد بیت یک از R2)

عکس ها رو ببینید

پیوست ها:

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

مهمان عزیز شما قادر به مشاهده پیوندهای انجمن مانشت نمیباشید. جهت مشاهده پیوندها ثبت نام کنید.

ارسال: #۱۴

RE: 2 سوال معماری (RTL و سیم Bus مشترک)

خیلی خیلی خیلی ممنونم ازتون. واقعا لطف کردید. نمیدونم چطور تشکر کنم. قول میدم انقدر این رو خوب بخونم که نمره خوب بیارم که پیش خودم وجدان درد نگیرم که انقدر زحمت دادم بهتون. این تنها کاری هست که از دستم بر میاد. باز هم ممنونم.

Can I see some ID?

Feeling left out?

نگران نباش، فقط روی این لینک برای ثبت نام کلیک کن. رمزت رو فراموش کردی؟ اینجا به یادت میاریم! close